- 您现在的位置:买卖IC网 > Sheet目录250 > SFCF2048H1BO2TO-I-M0-523-SMA (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 2G

�� �

�

�

�9.9.5� Bit� 3� (DRQ)�

�The� Data� Request� is� set� when� the� Card� requires� information� be� transferred� either� to� or� from� the� host� through� the�

�Data� register.� The� bit� is� cleared� by� the� next� command.�

�9.9.6� Bit� 2� (CORR)�

�This� bit� is� set� when� a� Correctable� data� error� has� been� encountered� and� the� data� has� been� corrected.� This�

�condition� does� not� terminate� a� multi-sector� read� operation.�

�9.9.7� Bit� 1� (IDX)�

�This� bit� is� always� set� to� ‘0’.�

�9.9.8� Bit� 0� (ERR)�

�This� bit� is� set� when� the� previous� command� has� ended� in� some� type� of� error.� The� bits� in� the� Error� register� contain�

�additional� information� describing� the� error.� In� case� of� read� or� write� access� commands� that� end� with� an� error,� the�

�address� of� the� first� sector� with� an� error� is� in� the� command� block� registers.� This� bit� is� cleared� by� the� next�

�command.�

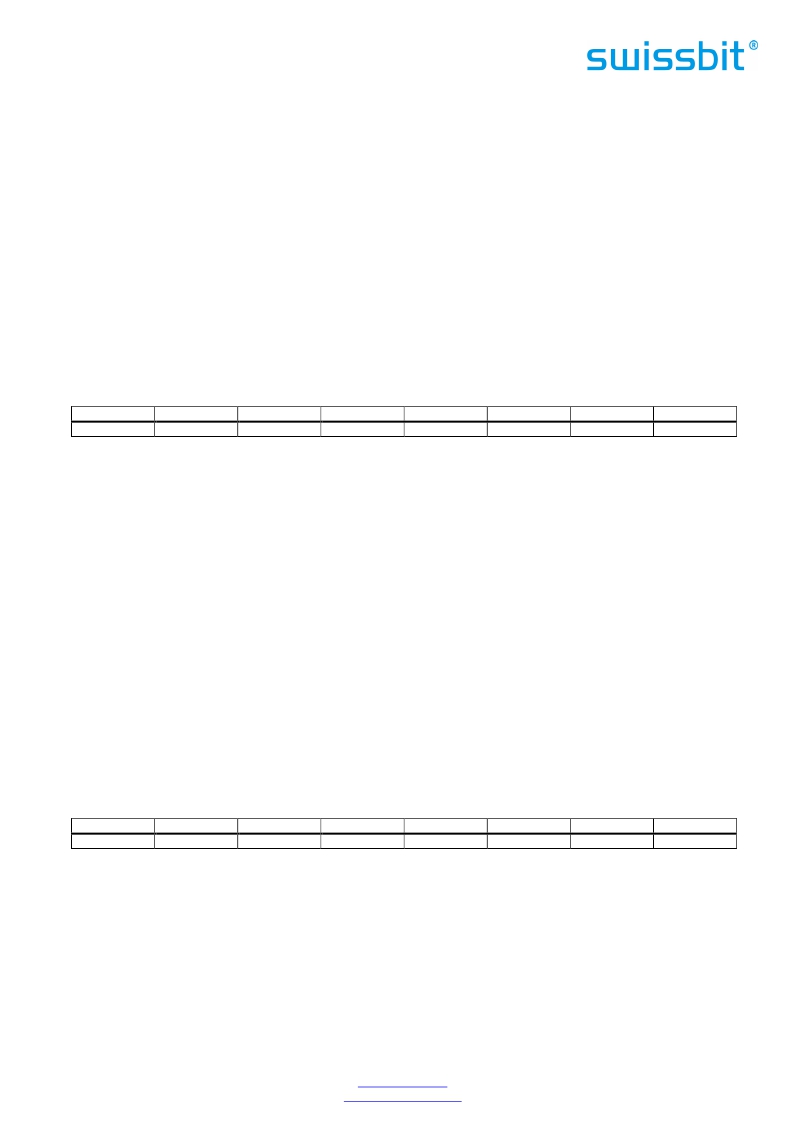

�Table� 53:� Status� &� Alternate� Status� Register�

�D7�

�BUSY�

�D6�

�RDY�

�D5�

�DWF�

�D4�

�DSC�

�D3�

�DRQ�

�D2�

�CORR�

�D1�

�0�

�D0�

�ERR�

�9.10� Device� Control� Register�

�The� Device� Control� register� is� located� at� address� 3F6h� [376h],� offset� Eh.�

�This� Write-only� register� is� used� to� control� the� CompactFlash� Memory� Card� interrupt� request� and� to� issue� an� ATA�

�soft� reset� to� the� Card.� This� register� can� be� written� even� if� the� device� is� BUSY.� The� bits� are� defined� as� follows:�

�9.10.1� Bit� 7� to� 3�

�Don’t� care.� The� host� should� reset� this� bit� to� ‘0’.�

�9.10.2� Bit� 2� (SW� Rst)�

�This� bit� is� set� to� 1� in� order� to� force� the� CompactFlash� Storage� Card� to� perform� an� AT� Disk� controller� Soft� Reset�

�operation.� This� clears� Status� Register� and� writes� Diagnostic� Code� in� Error� register� after� a� Write� or� Read� Sector� error.�

�The� Card� remains� in� Reset� until� this� bit� is� reset� to� ‘0.’�

�9.10.3� Bit� 1� (-Ien)�

�When� the� Interrupt� Enable� bit� is� set� to� ‘0’,� -� IREQ� interrupts� are� enabled.� When� the� bit� is� set� to� ‘1’,� interrupts� from�

�the� Card� are� disabled.� This� bit� also� controls� the� Int� bit� in� the� Card� Configuration� and� Status� Registe� r.� It� is� set� to� ‘0’�

�at� Power� On.�

�9.10.4� Bit� 0�

�This� bit� is� set� to� ‘0’.�

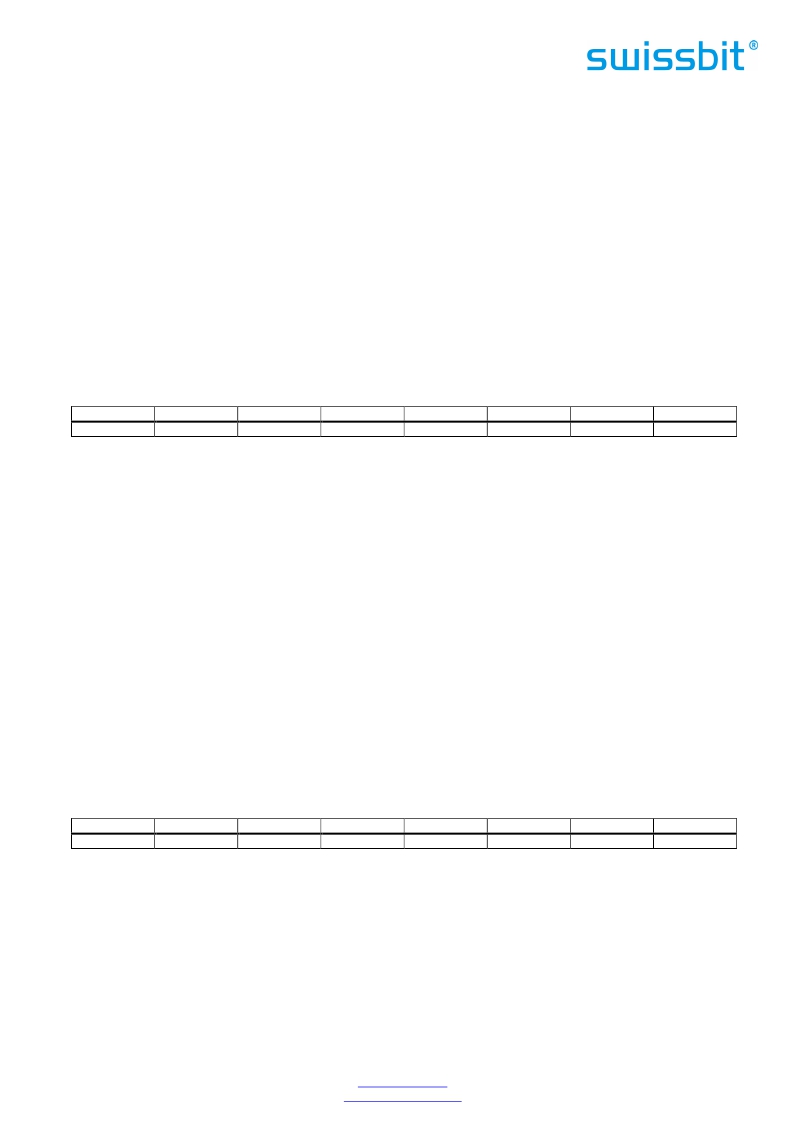

�Table� 54:� Device� Control� Register�

�D7�

�X(0)�

�D6�

�X(0)�

�D5�

�X(0)�

�D4�

�X(0)�

�D3�

�X(0)�

�D2�

�SW� Rst�

�D1�

�-Ien�

�D0�

�0�

�9.11� Card� (Drive)� Address� Register�

�The� Card� (Drive)� Address� register� is� located� at� address� 3F7h� [377h],� offset� Fh.�

�This� read-only� register� is� provided� for� compatibility� with� the� AT� disk� drive� interface� and� can� be� used� for�

�confirming� the� drive� status.� It� is� recommended� that� this� register� is� not� mapped� into� the� host’s� I/O� space� be� cause�

�of� potential� conflicts� on� Bit� 7.� The� bits� are� defined� as� follows:�

�9.11.1� Bit� 7�

�This� bit� is� don’t� care.�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.20�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-320_data_sheet_CF-HxBO_Rev120.doc�

�Page� 54� of� 101�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFCF4096H4BK2SA-I-QT-553-SMA

FLASH SLC UDMA/MDMA/PIO 4G

SFCF64GBH2BU4TO-I-NU-517-STD

FLASH SLC UDMA/MDMA/PIO 64GB

SFN08B4702CBQLF7

RES ARRAY 47K OHM 7 RES 8-DFN

SFP1050-12BG

FRONT END AC/DC 1050W 12V

SFP450-12BG

PWR SUP 450W 12V 36.6A W/STANDBY

SFSD1024N1BN1TO-I-DF-151-STD

FLASH MICRO SD CARD IND S-200 1G

SFSD2048L1BN2TO-I-DF-151-STD

FLASH SECURE DGTL CARD SD 2G

SFSD4096L1BN2TO-I-Q2-141-STD

FLASH SECURE DGTL CARD SDHC 4G

相关代理商/技术参数

SFCF2048H1BO2TO-I-M0-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H1BO2TO-I-M0-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-C-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H2BU2TO-I-MS-517-STD

功能描述:FLASH SLC UDMA/MDMA/PIO 2GB RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-440 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H2BU2TO-I-MS-527-STD

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-C-QT-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF2048H4BK1SA-I-QT-553-SMA

功能描述:FLASH SLC UDMA/MDMA/PIO 2G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-300 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF2048H4BK2SA-C-DS-553-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH SLC UDMA/MDMA/PIO 2G